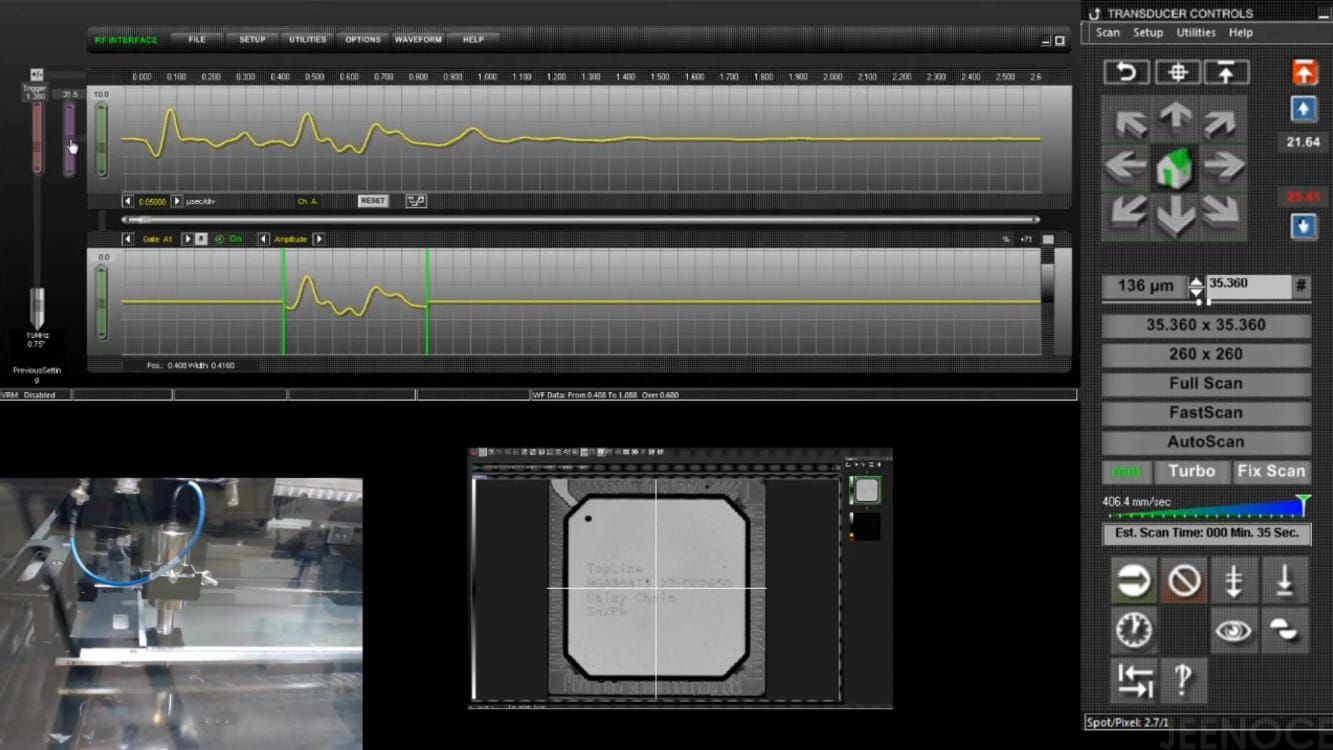

Ever wondered how to catch invisible defects before they wreck your chip yield? That’s where Scanning Acoustic Microscopy (SAM) steps in. SAM uses high-frequency sound waves to peer deep inside semiconductor packages without damaging them. Think of it as an ultrasonic camera that reveals hidden flaws like voids, delamination, and cracks—issues that often lead to costly chip failures.

By providing detailed acoustic impedance maps, SAM offers clear, actionable insights on internal structures. This non-destructive chip inspection technique lets engineers spot manufacturing problems early, paving the way for faster fixes and higher yields. Simply put, integrating SAM means fewer surprises, smoother production runs, and better overall quality.

At Jeenoce, we harness SAM technology to elevate semiconductor yield optimization, combining precision with ease of use in real-world environments. Whether you’re dealing with flip-chip underfill flaws or hybrid bonding quality control, understanding SAM’s basics positions you to unlock greater value throughout your chip manufacturing process.

In chip manufacturing, even small defects can kill your yield. Things like voids, delaminations, cracks, and packaging flaws are some of the usual suspects that lead to chip failures. These hidden issues often happen during assembly and packaging, causing problems like flip-chip underfill flaws or poor hybrid bonding quality that you can’t see with the naked eye.

This is where Scanning Acoustic Microscopy (SAM) shines. It uses ultrasonic void detection and acoustic impedance mapping to catch these defects early, without damaging the chips. SAM’s non-destructive chip inspection helps spot wafer-level issues and SMT line defects before they grow bigger. Whether it’s delamination analysis in packaging or checking for flip-chip underfill voids, SAM microscope technology gives you a clear picture of hidden problems that would otherwise slip through.

By identifying these yield killers early, SAM helps prevent costly rework and scrap, making your semiconductor yield optimization more effective and efficient.

Improving chip manufacturing yield with Scanning Acoustic Microscopy (SAM) starts with a clear plan. Here’s how to get it done step-by-step:

Review your current chip production process.

Identify common defect points like flip-chip underfill flaws or delamination areas.

Make sure your teams know the benefits of SAM and are ready to adapt.

Set realistic goals for yield improvement based on past data.

Install SAM microscopes directly on your Surface Mount Technology (SMT) lines.

Ensure the SAM equipment is compatible with your existing setup for smooth operation.

Train operators on using SAM for scanning wafers and packaged chips.

Use hybrid bonding quality control features to catch defects early.

Use SAM’s acoustic impedance mapping and ultrasonic void detection to inspect chips without damage.

Run scans while the chips move along the production line to keep processes fast.

Monitor for common yield killers like voids, cracks, and delamination with non-destructive chip inspection tools.

Immediately analyze data for fast decision-making.

Look at the scan results to pinpoint where defects occur most.

Adjust process parameters, soldering temps, or material choices based on SAM feedback.

Run targeted inspections on suspicious batches using wafer-level NDT techniques to confirm improvements.

Keep tracking results to see which fixes truly boost yield.

Once SAM integration shows positive impact, expand its use to other production lines or fabs.

Validate improvements with consistent yield reports and quality metrics.

Use real-world case studies and collected data to justify further investments.

Continue refining your approach using SAM-enabled insights for sustainable semiconductor yield optimization.

Following these steps helps you get the most from acoustic microscopy and scanning acoustic tomography techniques, turning your chip manufacturing into a more efficient, less wasteful process.

Scanning Acoustic Microscopy (SAM) has proven its value in many chip fabs across China and Southeast Asia, helping manufacturers boost semiconductor yield optimization by spotting defects early.Here are some real examples where SAM made a difference:

Early Void Detection: One fab used SAM’s ultrasonic void detection to find hidden voids in flip-chip packages before they caused failures. This non-destructive chip inspection step cut rework rates by 20%, saving significant production time and cost.

Delamination Analysis: Another facility applied SAM to identify delamination in packaging materials that traditional optical inspection missed. This acoustic microscopy allowed quick correction, improving overall packaging reliability and yield.

Flip-Chip Underfill Flaw Spotting: A major chip maker integrated SAM on their SMT line to scan for underfill flaws in flip-chip assemblies. These issues were flagged immediately, preventing defective batches from moving forward.

Hybrid Bonding Quality Control: Using acoustic impedance mapping through SAM, a fab optimized hybrid bonding processes by detecting bonding inconsistencies that were tough to catch otherwise. This led to measurable increases in wafer-level NDT pass rates.

These stories show how SAM microscope technology can stop yield killers right at the source and keep chip manufacturing running smoother. For China and Southeast Asia-based fabs, adopting SAM means less waste, faster throughput, and higher quality chips ready to meet market demands.

When using Scanning Acoustic Microscopy (SAM) for chip manufacturing, getting a strong return on investment (ROI) means following best practices and avoiding common traps. Here’s what I’ve found helps maximize value with SAM without wasting time or money.

Start with Clear Goals

Define exactly what defects you want to catch early—like ultrasonic void detection or delamination analysis in packaging. Knowing your focus helps tailor your SAM microscope setup and speeds up results.

Train Your Team Thoroughly

SAM is powerful but requires skilled operators. Investing in training means quicker, more accurate scans and better acoustic impedance mapping to spot even subtle issues.

Integrate Seamlessly into SMT Lines

Align your SAM hardware with existing surface-mount technology (SMT) lines or wafer-level NDT techniques. Real-time defect scanning keeps your chip production moving and reduces downtime.

Use Data to Drive Continuous Improvement

Analyze inspection data regularly to identify trends or recurring defects. Optical and acoustic microscopy results paired together can guide improvements in process controls and hybrid bonding quality control.

Plan for Scale Up and Validation

Once you have solid data and processes, gradually increase your inspection volumes. Validate results to make sure yield improvements are consistent.

Poor Workflow Integration

Don’t treat SAM as an afterthought. If you place it outside your main production flow, you’ll lose time and miss early detection benefits.

Neglecting Equipment Maintenance

Acoustic microscopy tools need routine calibration and inspections. Skipping maintenance can cause inaccurate readings and missed hidden defects.

Overloading Operators with Data

SAM generates a lot of imaging data. Without clear procedures or software to filter and prioritize defects, operators can get overwhelmed and slow down decision-making.

Ignoring Collaboration Between Teams

Yield improvements rely on open communication between quality, engineering, and production teams. Without that, SAM findings might not translate into actionable fixes.

Following these guidelines and steering clear of these missteps will help your chip fab fully leverage scanning acoustic tomography and other wafer-level NDT techniques. That means fewer failures, higher semiconductor yield optimization, and a healthier bottom line.

When it comes to boosting your chip manufacturing yield with Scanning Acoustic Microscopy, having the right partner makes all the difference. Jeenoce specializes in delivering customized SAM solutions designed to fit your unique production needs. Whether you’re looking to integrate SAM hardware seamlessly into your SMT lines or need expert support for ultrasonic void detection and delamination analysis, Jeenoce has you covered.

Why choose Jeenoce?

Custom integration with your existing processes, minimizing downtime

Expertise in non-destructive chip inspection and real-time defect scanning

Proven track record in helping semiconductor fabs optimize yields through acoustic impedance mapping and hybrid bonding quality control

Support tailored for the Southeast Asia wafer fabs, focusing on efficiency and return on investment

Working with Jeenoce means you get more than just acoustic microscopy tools—you gain a trusted partner ready to help scale, optimize, and validate your yield improvement efforts. If you want to get the most out of Scanning Acoustic Tomography technology and stay ahead in the competitive chip market, Jeenoce’s tailored SAM solutions are the smart move.

Message